Technologies (logiques)

Historiquement les circuits à commutation (changement d’état de portes en cascade pour réaliser des fonctions complexes) ont fait appel à plusieurs technologies qui ont suivies les avancées des semi-conducteurs. Initialement, le technologie TTL, basée sur les transistors bipolaires a permis la réalisation des premières portes sous la forme de circuits intégrés. Puis les technologies ont évolué progressivement, soit en utilisant les transistors bipolaires différemment comme dans la logique ECL (Emitter Coupled Logic) qui donne toujours une très grandes vitesses de commutation, soit en utilisant les transistors à effet de champ (FET) et en particulier des FET-CMOS qui a donnée son nom à la logique CMOS, aujourd’hui la plus courante.

Un élément important à noter est que quelque soit la technologie utilisée, tous les transistors fonctionnent en mode tout-ou-rien / passant-bloquant, on dit aussi qu’ils sont saturés. En effet, pour obtenir des valeurs précises en sortie, il est important de ne pas utiliser les transistors dans leur zones linéaires (comme on le ferait par exemple pour un amplificateur). On parle d’ailleurs dans ce cas d’électronique linéaire que l’on oppose à notre sujet d’électronique digitale ou numérique (en bon français).

Chaque logique présente des tensions de fonctionnement différentes et parfois chaque constructeur apporte des améliorations spécifiques qui peuvent faire varier les tensions détectées ou produites par ces circuits. Il est donc plus que recommandé de lire les documents édités par les fabricants de semi-conducteur. Comme on le verra plus loin, les circuits sont généralement compatibles entre eux, mais il faut parfois savoir vérifier cette compatibilité ou assurer une adaptation quand cela est nécessaire, en particulier quand des logiques utilisant des tensions différentes doivent communiquer, par exemple, un processeur 3,3v devant commander un périphérique en 5v.

Entrées (tout-ou-rien)

Les entrées auxquelles on va s’intéresser ici, n’ont que 2 états. Ce sont des entrée binaires qui détectent un état BAS ou un état HAUT. Ces entrées sont à distinguer des entrées analogiques qui fonctionnent sur toute une plage continue de valeurs.

Schéma de réalisation

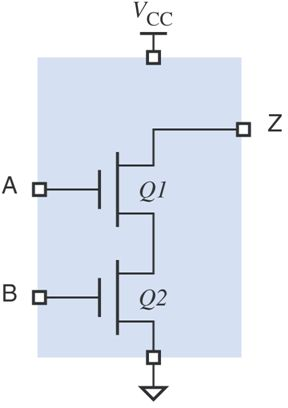

Voici un schéma classique d’une entrée CMOS :

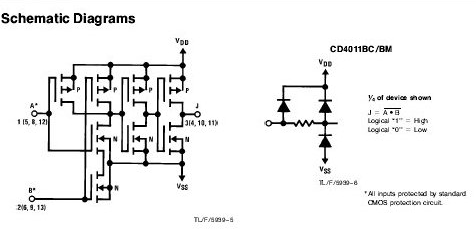

Sur la gauche, vous pouvez constater que les transistors sont connectés par paires complémentaires (N et P) sur les 2 entrées A et B ; chacun étant passant soit au niveau BAS, soit au niveau HAUT de l’entrée. Les étage suivants correspondent à la fonction logique assurée.

On notera les diodes de protection présentées à droite qui sont placées sur chaque entrée. Elles protèges les Gate des FET des tensions supérieures à la tension d’alimentation (Vdd) ou négatives (inférieures à Vss). Elles protègent aussi des décharges électrostatiques qui détruisent souvent les transistors.

A noter que les appellations Vdd et Vss, sont parfois utilisées pour indiqué la tension liée au Drain du transistor et celle liée à la Source. Il s’agit bien de Vcc et GND sur les autres représentations.

Niveaux d’entrée

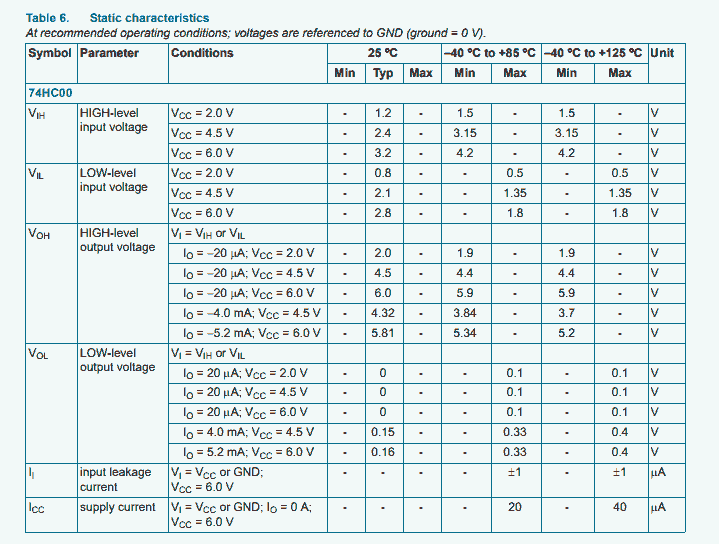

Voici un extrait d’une fiche de caractéristiques statiques d’un circuit classique (HC : Highspeed CMOS) :

La partie qui nous intéresse ici ne concerne que les « input voltage » dont on voit que les niveaux dépendent, logiquement, de la tension d’alimentation (Vcc), ainsi que de la température du circuit.

Si l’on travaille dans les conditions normales du bricoleur, on se limitera à la tension de 4,5v (la plus proche de 5v) et la température de 25°C. Les valeurs qui nous intéressent sont les « Typ » (typiques) qui correspondent à des valeurs moyennes obtenues sur des échantillons du constructeur. Cela signifie que votre circuit (DUT : Device under Test) à des valeurs proches de celles-ci dans un intervalle que le constructeur n’a pas spécifié ici (5 à 10% souvent).

Ici les paramètres VIH et VIL, respectivement « seuil de tension d’entrée du niveau HAUT » et donc « seuil de tension d’entrée du niveau BAS » sont à 2,4v et 2,1v. Cela indique que toute tension d’entrée inférieure à 2,1v sera considérée comme un état BAS alors que toute tension d’entrée supérieure à 2,4v sera considérée comme un état HAUT. De 2,1 à 2,4v l’entrée n’aura pas d’état précis défini, peut-être HAUT, peut-être BAS, peut-être oscillant entre les deux. C’est une zone dans laquelle l’entrée ne doit pas se trouver.

Résistances de tirage (ou de rappel)

Si une entrée est laissée volante et n’est pas associée à une tension particulière, il existe un risque de commutation incontrôlée.

Toute entrée doit être fixée à un potentiel HAUT ou BAS.

Parfois l’un des état, du fait de la technologies de la porte est plus consommateur que l’autre ; c’était particulièrement vrai pour les entrées des portes TTL qui consommaient moins quand elles étaient « tirées » au Vcc. Ce n’est plus le cas sur les entrées des portes CMOS qui ont des courants d’entrée négligeables. Il reste toutefois recommandé de lier les entrées libres au Vcc ou au 0v (GND) via une résistance d’une 10ène de KOhm, et non directement au GND ou au Vcc.

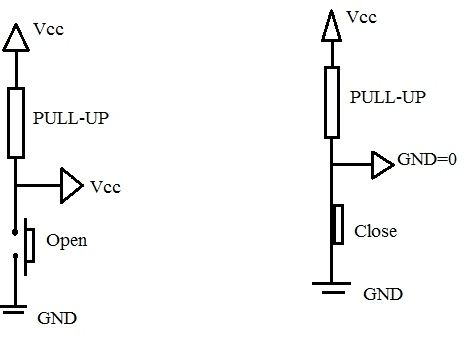

Un cas d’usage classique correspond à l’utilisation d’un contact sec relié à une entrée :

Si l’on n’utilise pas de résistance de tirage, l’entrée se trouve flottante tant que l’interrupteur n’est pas pressé. Elle n’a de potentiel défini (ici GND) que lorsque l’interrupteur est fermé. En ajoutant la résistance de tirage, l’entrée voit sa tension appliquée « tirée » vers Vcc.

Sorties

De même que précédemment, on va s’intéresser aux sorties « tout-ou-rien » qui ne possèdent que 2 états, toujours les mêmes, HAUT et BAS.

Si l’on reprend le schéma 1, ci-dessus, on voit que les transistors de sortie sont aussi complémentaires et appairés. C’est à dire que l’un ou l’autre est passant à un instant donné et que la sortie est donc reliée soit au Vdd, soit au Vss, mais en aucun cas les deux en même temps car cela produirait un court-circuit entre Vcc et GND et détruirait le circuit par surchauffe.

Niveaux de sortie

Les caractéristiques de transistor n’étant pas parfaites, il apparaît que chaque transistor de sortie va présenter une faible résistance de sortie lorsqu’il est passant et une résistance grande mais pas infinie quand il est bloqué. Il en résulte donc que la sortie ne va pas varier de Vcc à GND mais dans une plage de tension entre ces valeurs.

C’est ce qu’indique le constructeur dans les lignes « output level » du tableau 1. La ligne VOH indique les valeurs minimum d’une sortie, pour les conditions correspondantes (VI = VIH ou VIL, c’est à dire que les entrées à des états définis ; 25°C).

Pour une sortie à l’état HAUT, le tableau précise maintenant 2 réponses en fonction du courant de sortie (valeur négative) :

- -20 µA : (courant quasi nul) la sortie est garantie d’au-moins 4,5v pour une tension

Vccde la même valeur : il n’y pas de perte dans le transistor ; - -4.0 mA : (courant moyen) la sortie est d’au-moins 4,32v et donc légèrement inférieure à la tension de

Vcc; cela montre la perte dans le transistor qui reste légèrement résistif.

Il en est de même pour une sortie à l’état BAS et pour les mêmes valeurs de courant entrant cette fois (valeur positive) :

- 20 µA : la sortie est garantie à 0 (

GND), sans perte donc ; - 4.0 mA : la sortie est d’au-plus de 0,15v et donc légèrement supérieure à

GND.

On peut d’ailleurs constater que, bien que le schéma soit symétrique, les portes ne le sont pas dans leurs tensions de sortie.

Ce qui reste intéressant, c’est que dans toutes les conditions, les valeurs de sortie sont conforment aux intervalles d’entrée, ce qui permet, à tension d’alimentation égale, la cascade des circuits d’une même famille sans adaptation ; et c’est heureux.

Les autres lignes du tableau 1, nous indique que les entrées ont un courant de fuite de l’ordre de +/- 1 µA de fuite dans les cas de températures les plus défavorables et que l’on peut donc commander plusieurs entrées avec une seule sortie.

Application Numérique :

– Une sortie peut délivrer ou absorber 4 mA ;

– Une entrée fuit de l’ordre de +/- 1 µA ;

On peut donc commander 4000 entrées avec une seule sortie en respectant les plages de tension.

Sorties à collecteur ouvert

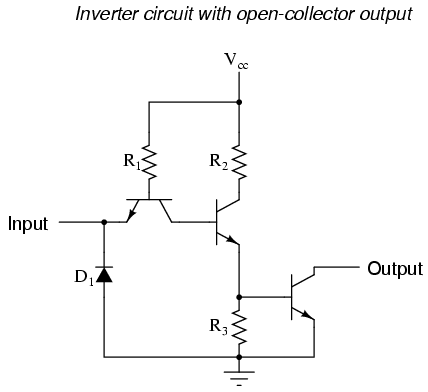

Il existe un type de sorties particulier où un seul des deux transistors de la paire est utilisé. Cela permet à la sortie d’avoir un comportement identique à un contact sec, et à l’aide de la tension de tirage adaptée, de commuter une tension différente de celle du circuit. Voici un exemple d’inverseur avec des transistors bipolaires (donc pas FET) :

Dans ce cas quand le transistor de sortie est passant, la sortie (Output) est tirée var le GND, mais quand il est bloqué, il n’y a plus de tension appliquée à la sortie : elle est donc libre de potentiel et flottante. L’ajout d’une résistance de tirage permet de garantir que cette sortie se trouvera à un autre potentiel défini par cette résistance.

Il en va de même avec les transistors FET, dans un schéma similaire qui porte parfois le nom de sortie à « drain-ouverte », puisque c’est le nom de la broche libre du transistor FET (ici une porte NON-ET) :